3 나노 시대: 반도체 기술의 새로운 전환점:

3 나노(3nm) 공정은 반도체 기술에서 중요한 이정표를 의미합니다. 이는 트랜지스터의 크기가 3 나노미터로 축소된 제조 기술로, 반도체 소자의 성능을 극대화하고 전력 효율성을 높이는 데 중요한 역할을 합니다. 이 공정은 전 세계 반도체 산업에서 매우 중요한 기술적 진전을 의미하며, 특히 고성능 컴퓨팅(HPC), 인공지능(AI), 모바일 기기 등 다양한 분야에서 그 필요성이 크게 대두되고 있습니다.

3 나노 공정은 이전 세대인 5 나노 공정보다 약 1.7배 더 높은 트랜지스터 밀도를 제공하며, 동일한 성능에서 전력 소모를 25~35% 줄일 수 있습니다. 이는 더 작은 크기에서 더 많은 성능을 제공하면서도 전력 소모를 줄여 전자 기기의 배터리 효율성을 크게 향상할 수 있다는 의미입니다.

TSMC 3 나노 공정:

세계 최대 반도체 파운드리 기업인 TSMC(대만반도체제조회사)는 3 나노 공정 기술을 선도하고 있습니다. TSMC의 N3 공정은 2022년 말부터 대량 생산에 들어갔으며, 성능, 전력 효율성, 트랜지스터 밀도에서 큰 향상을 이루었습니다. 특히 TSMC는 여러 변형된 3 나노 공정을 제공하는데, N3E는 개선된 수율과 더 나은 제조 안정성을 제공하며, N3P와 N3X는 고성능 및 모바일 기기, AI 처리에 최적화된 기술입니다.

TSMC의 3 나노 공정은 FinFET 아키텍처를 기반으로 하며, 이는 이전의 5 나노 공정과 비교했을 때 트랜지스터의 성능을 크게 향상할 수 있습니다. 또한 TSMC는 "FinFLEX"라는 기술을 도입하여, 다양한 트랜지스터 유형을 혼합하여 칩 내에서 최적의 성능을 낼 수 있도록 했습니다.

TSMC 3나노 시대의 기술적 문제:

3 나노 3 나노 공정은 매우 세밀한 제조 과정을 요구하며, 이를 위해 EUV(Extreme Ultraviolet) 리소그래피 기술과 같은 고급 장비들이 사용됩니다. 그러나, 공정이 미세화됨에 따라 여러 기술적 문제도 발생하고 있습니다. 가장 큰 문제는 트랜지스터의 전력 누설과 발열 문제입니다. 3 나노 크기의 트랜지스터는 전력 효율을 높이는 동시에 발열을 최소화해야 하는데, 이 두 가지를 동시에 만족시키는 것이 매우 어렵습니다.

또한, 3 나노 공정에서의 수율 문제도 중요한 기술적 과제입니다. 초기 생산에서 수율이 낮을 수 있으며, 이는 대량 생산을 위한 큰 장애물로 작용합니다. TSMC는 N3E 공정을 통해 수율을 개선하기 위해 많은 노력을 기울였으나, 3 나노 공정의 높은 복잡성으로 인해 일정 부분에서 수율 문제는 계속 발생하고 있습니다.

TSMC 3나노 공정 강점과 현재 수율:

TSMC의 3나노3 나노 공정은 높은 트랜지스터 밀도와 향상된 전력 효율성을 제공하는 강점을 가지고 있습니다. 특히 N3E 공정은 제조 과정에서의 안정성을 높여 수율 개선에 큰 기여를 했습니다. 이에 따라, TSMC는 2023년부터는 3 나노 공정의 대량 생산에 착수할 수 있었고, 주요 고객인 애플, 퀄컴, AMD 등에게 공급을 시작했습니다.

하지만, 수율 향상은 여전히 중요한 과제입니다. N3 공정의 초기 수율은 약간 낮았으나, 시간이 지남에 따라 수율은 점진적으로 개선되었습니다. 특히 N3E 공정은 안정성과 수율 개선을 위해 디자인과 제조 공정을 최적화하여 더 나은 결과를 도출하고 있습니다.

국내 3나노 공정 기술적 문제점:

한국은 삼성전자가 3 나노 공정을 개발하고 있으며, 이를 통해 글로벌 반도체 시장에서 경쟁력을 강화하려고 하고 있습니다. 그러나 국내에서도 몇 가지 기술적 문제들이 존재합니다. 삼성전자는 3 나노 공정에서의 기술적 문제로 EUV 공정의 복잡성, 트랜지스터 누설 전류 문제, 그리고 수율 문제를 겪고 있습니다. 특히, EUV 리소그래피 장비의 정밀한 제어가 어려워 복잡한 구조를 구현하는 데 어려움이 있으며, 이로 인해 초미세 공정에서의 품질 안정성이 떨어질 수 있습니다.

또한, 삼성전자의 경우 3 나노 공정에서의 수율 개선을 위해서는 더 많은 기술적 혁신이 필요합니다. 공정 초기에 발생한 수율 문제를 해결하기 위해서는 공정의 최적화와 함께, 새로운 물질이나 새로운 아키텍처의 도입이 필요할 수 있습니다.

국내 3나노 공정 수율 향상을 위한 최우선 보완점:

국내 3나노 공정의 수율 향상을 위한 최우선 보완점은 제조 공정의 안정성 강화와 트랜지스터 성능의 개선입니다. 삼성전자는 EUV 리소그래피 공정을 더욱 정밀하게 제어하고, 트랜지스터 구조를 최적화하여 누설 전류를 최소화하는 방향으로 기술 개발을 진행하고 있습니다.

3나노 공정 국내외 개발 현황:

국내외에서 3 나노 공정 개발은 활발히 진행되고 있으며, 특히 TSMC와 삼성전자는 각각 자사의 3 나노 공정을 상용화하는 데 큰 진전을 이루었습니다. TSMC는 N3E 공정을 기반으로 한 대량 생산을 시작했고, 삼성전자는 3 나노 공정을 첫 번째로 선보였습니다. 다른 기업들도 차세대 기술인 GAAFET(게이트 올 어라운드 FET)을 도입하려는 시도를 하고 있으며, 이는 3 나노보다 더 작은 2 나노 공정으로 발전할 것입니다.

결론적으로, 3 나노 공정은 반도체 산업의 혁신을 이끄는 중요한 기술로 자리 잡고 있으며, 이는 전력 효율성, 성능, 트랜지스터 밀도의 향상에 기여하고 있습니다. TSMC와 삼성전자는 각기 다른 기술적 문제를 해결하고 있으며, 이들은 3 나노 공정의 상용화와 확산에 중요한 역할을 하고 있습니다.

삼성의 EUV 기술 향상을 위한 노력:

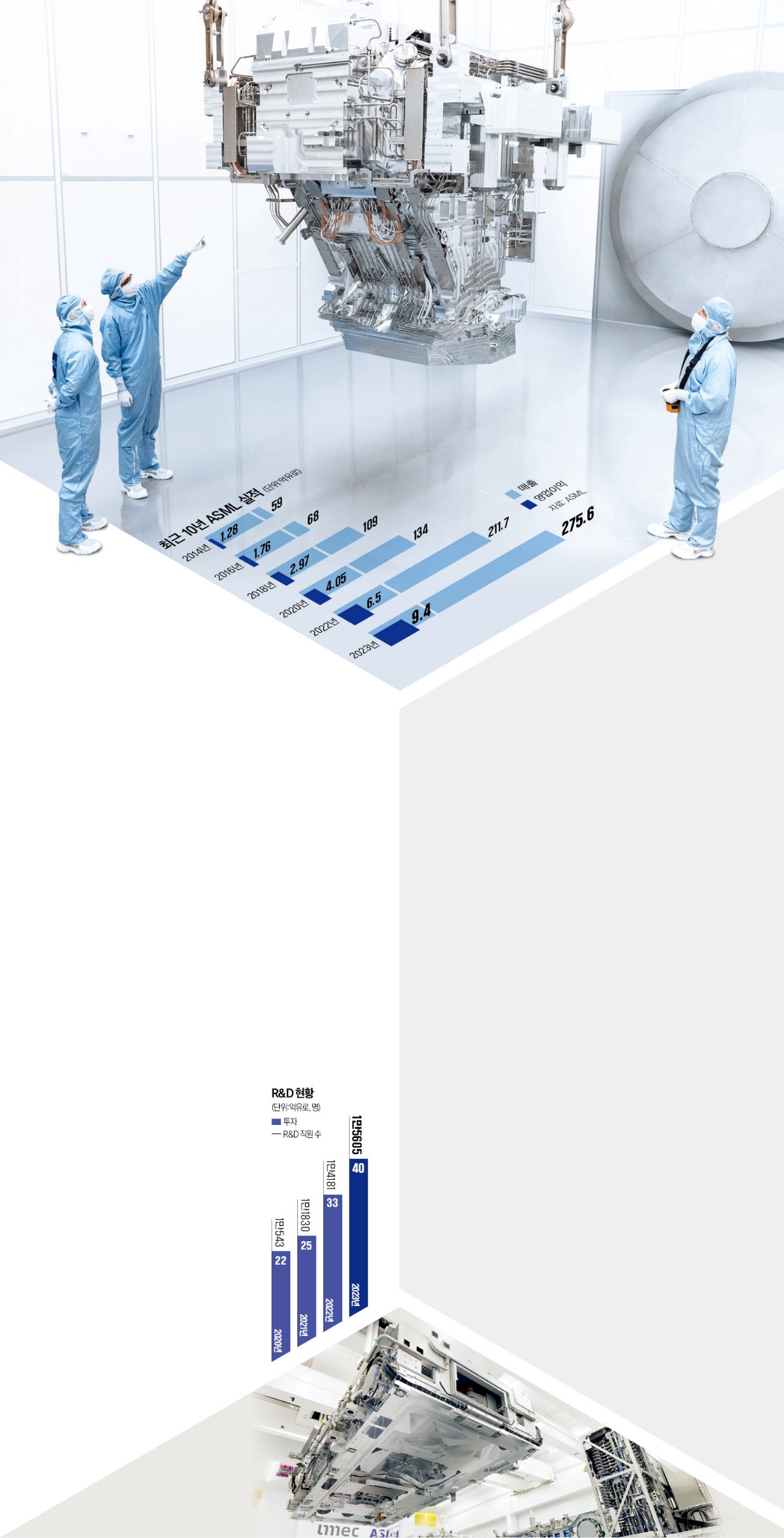

삼성은 EUV(Extreme Ultraviolet) 기술에 상당한 투자를 진행하고 있습니다. 2024년에는 삼성전자가 ASML과 협력하여 차세대 EUV 리소그래피 기술을 이용한 첨단 반도체 제조를 위한 연구소를 설립하기로 했습니다. 이 연구소는 한국 내에 위치하며, 총 1조 원 규모의 투자가 이루어질 예정입니다.

삼성은 EUV 기술을 활용해 메모리 반도체뿐만 아니라, 고급 로직 반도체의 생산에서도 중요한 성과를 거두고 있습니다. 또한 삼성은 EUV 기술을 적용한 DRAM 생산을 세계 최초로 성공시키며, EUV 기술을 고도화한 제품들을 시장에 출시하였습니다.

하지만, 삼성은 EUV 장비의 도입에 있어 일정한 어려움을 겪고 있습니다. 2024년 10월, 삼성은 미국 텍사스에 있는 공장에 대한 EUV 장비 도입을 연기했습니다. 이로 인해 해당 공장의 운영 시작이 예상보다 지연될 것으로 보입니다.

그럼에도 불구하고, 삼성은 EUV 기술을 기반으로 한 차세대 반도체 공정 개발에 큰 비중을 두고 있으며, 미국의 반도체 산업 클러스터에 대한 대규모 투자를 이어가고 있습니다.

따라서 삼성은 EUV 기술을 중심으로 반도체 생산의 고도화와 경쟁력 강화를 위해 지속적인 투자와 기술 개발을 추진하고 있습니다.

개인적으로 K-반도체를 이끌어가는 우리의 기업들은 반드시 세계의 시장에서 한국인의 위대한 저력을 보여 주리라 확신합니다.

'반도체' 카테고리의 다른 글

| 삼성전자, '7세대 QLC(Quad-Level Cell) V-NAND' 플래시 메모리 기술혁신! (4) | 2024.12.20 |

|---|---|

| 차세대 고성능 초저전력 상변화 메모리 소자PCM! (3) | 2024.12.13 |

| 차세대 고성능 반도체, Extended BEOL (3) | 2024.12.11 |

| 무어의 법칙의 한계점과 현대 반도체 기술 발전 (4) | 2024.12.10 |

| 경쟁속 의 상생, LPDDR 메모리를 베이스로 하는 PIM 메모리의 기술 (2) | 2024.12.04 |