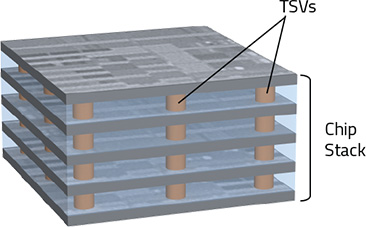

▶TSV 공정의 개념:

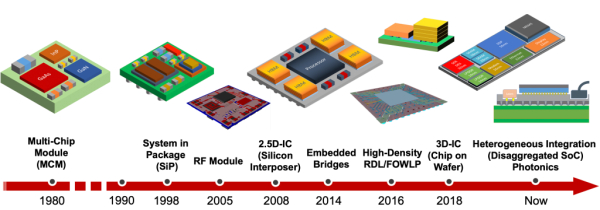

Through-Silicon Via(TSV)는 반도체 칩을 수직으로 연결하기 위해 실리콘 기판에 형성된 마이크로미터 크기의 수직 구멍입니다. 이 기술은 2.5D 및 3D 집적 회로(IC) 패키징에 사용되며, 회로 간 거리를 줄이고 전기적 성능을 향상해 높은 데이터 전송 속도와 저전력 소모를 가능하게 합니다. TSV는 특히 고성능 컴퓨팅, 이미지 센서, 메모리 스태킹 등에 필수적이며, SoC와 같은 모놀리식 접근법 대비 빠르고 유연한 시스템 통합을 제공합니다.

TSV는 일반적으로 실리콘 웨이퍼에 구멍을 뚫고, 구멍에 금속(보통 구리)을 채워 전기적인 연결을 생성하는 공정을 따릅니다. TSV가 형성된 후 웨이퍼는 원하는 형태로 연마되고, 다이와 다이를 수직으로 연결하여 통신을 수행하는 다층 구조가 완성됩니다. 이로 인해 기존의 와이어 본딩 방식에서 오는 RC 지연 문제를 해결하고 신호 손실을 최소화할 수 있습니다.

▶TSV 공정에 필요한 기술:

TSV 공정을 구성하는 주요 기술은 다음과 같습니다.

▶실리콘 에칭 및 드릴링:

TSV의 가장 첫 번째 단계는 웨이퍼에 마이크로미터 단위의 구멍을 형성하는 것입니다. 실리콘 에칭은 일반적으로 반응성 이온 에칭(RIE) 공정을 사용하여 이루어지며, 구멍의 깊이와 형태를 제어하여 균일한 수직 구조를 만듭니다. 에칭의 정확도와 미세한 제어는 TSV의 신뢰성 및 성능에 큰 영향을 미칩니다.

▶절연층 형성:

구멍을 뚫은 후에는 구멍 벽면에 절연층을 형성해야 합니다. 주로 SiO₂나 SiN을 사용하여 구리와 실리콘 간의 전기적 절연을 보장합니다. 절연층의 두께와 균일성은 TSV의 전기적 특성과 신뢰성에 결정적입니다.

▶금속 충전 및 구리 도금:

절연이 완료된 후, TSV는 주로 구리를 이용하여 금속으로 충전됩니다. 구리 도금은 전기적 연결을 위한 핵심 기술로서, 고속 구리 도금 공정과 구리의 확산을 막기 위한 적절한 버퍼층이 필요합니다. 불량 도금은 공정 오류를 초래할 수 있으며, 전기적 신뢰성에 큰 영향을 미칩니다.

▶웨이퍼 레벨 패키징과 연마 공정:

TSV 형성 후, 웨이퍼를 평탄하게 만들기 위해 연마 공정이 수행됩니다. 주로 화학 기계적 연마(CMP) 공정을 통해 표면을 매끄럽게 하며, 다른 층과의 접합을 가능하게 합니다. 이때 평탄화 정도와 연마 균일성은 TSV 구조의 기계적 안정성 및 연결 신뢰성에 필수적입니다.

▶TSV 공정의 몰딩과 신뢰성 문제:

TSV는 특유의 몰딩 및 신뢰성 문제를 동반합니다.

▶몰딩 과정에서 발생하는 응력 문제:

TSV는 금속과 실리콘의 열팽창 계수 차이로 인해 열응력 발생이 불가피합니다. 특히, 구리와 실리콘의 열팽창 계수가 다르므로 온도 변화에 따른 응력이 TSV 주위에 집중되며, 이로 인해 크랙이나 층간 박리가 발생할 가능성이 있습니다. 이를 해결하기 위해 TSV 주변에 응력 완화를 위한 중간층을 삽입하거나 구리의 특성을 개선하는 접근이 연구되고 있습니다.

▶전기적 및 열적 신뢰성 문제:

TSV는 고속 데이터 전송 및 저전력 소모를 가능하게 하지만, 전기적 열화 현상이 발생할 수 있습니다. 이는 TSV의 저항이 시간이 지남에 따라 증가하여 신호 지연 및 성능 저하를 유발할 수 있습니다. 또한, 높은 전류 밀도와 열이 발생하면서 금속 확산이나 일렉트로마이그레이션과 같은 문제가 발생할 수 있어 TSV의 장기 신뢰성을 저하시킬 우려가 있습니다.

▶TSV 공정의 국내외 개발 현황:

▶국내 개발 현황:

한국에서는 삼성전자와 SK하이닉스가 TSV 기술에 대해 선도적인 위치를 차지하고 있으며, 특히 메모리 스택과 HBM(High-Bandwidth Memory)와 같은 고성능 메모리 솔루션에 TSV를 적용하고 있습니다. 이를 통해 AI와 데이터 센터 시장에서의 경쟁력을 강화하고 있으며, 국내 연구기관에서도 TSV의 신뢰성과 열적 특성을 개선하는 연구가 활발히 진행 중입니다.

▶국제 개발 현황:

국제적으로는 TSMC, 인텔, 퀄컴 등도 TSV 기술을 활용하여 고성능 패키징 솔루션을 개발하고 있습니다. 특히 TSMC는 3D 패키징 기술을 통해 프로세서와 메모리 간의 통합을 개선하고, 인텔은 EMIB(Embedded Multi-Die Interconnect Bridge)와 같은 기술을 통해 다이 간 통신을 강화하고 있습니다. 유럽과 일본에서도 3D 스태킹 연구가 활발하게 진행되고 있으며, TSV 기술은 다양한 전자기기 및 서버, 통신장비에 폭넓게 활용되고 있습니다.

▶TSV 공정의 개선 필요 사항:

TSV 공정에서 주요 개선 사항은 다음과 같습니다.

▶열 및 응력 관리 기술 개선:

TSV 주변의 응력 완화와 열 관리를 위해 고성능 절연재 및 방열재의 개발이 필요합니다. 이를 통해 TSV 구조의 장기 신뢰성을 높이고 고온에서의 안정성을 확보할 수 있습니다.

▶신뢰성 검증 시스템의 고도화:

TSV의 신뢰성을 평가하는 시스템의 정확도와 속도를 향상하여, 미세 공정에서 발생할 수 있는 결함을 조기에 탐지하는 기술이 필요합니다. 이를 통해 수율을 개선하고 대량 생산에서의 문제를 줄일 수 있습니다.

▶재료 및 공정 개선:

구리의 일렉트로마이그레이션을 방지하기 위한 고급 재료 연구가 진행되고 있으며, 웨이퍼 및 다이의 두께를 줄여 공정 효율성을 높이고 전기적 성능을 강화하는 방향으로 연구가 이루어지고 있습니다.

'반도체' 카테고리의 다른 글

| 반도체 전쟁 승리를 위한 2나노공정! (5) | 2024.11.02 |

|---|---|

| 반도체의 핵심 기술,이종집적! (4) | 2024.11.01 |

| 성능과 수율 두 마리 토끼를 잡는 칩렛 기술! (3) | 2024.10.28 |

| 메모리의 혁신, 인 메모리 컴퓨팅! (12) | 2024.10.28 |

| AI에 최적화된 메모리,TPU! (12) | 2024.10.26 |